Hardware Architecture

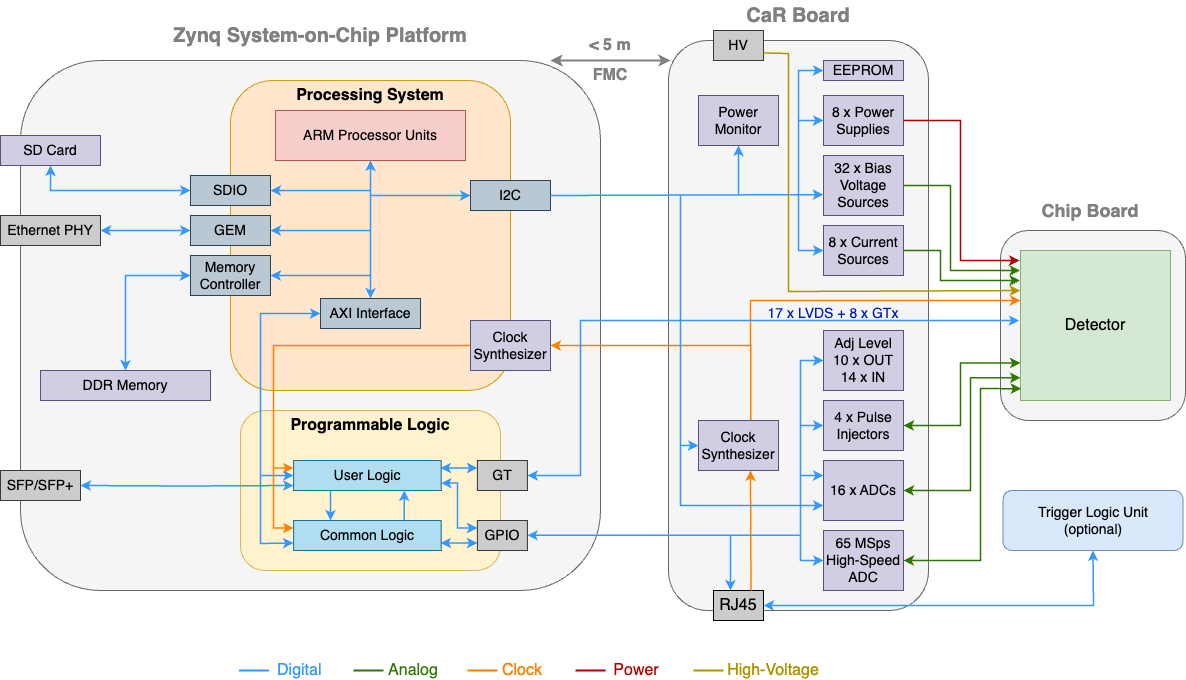

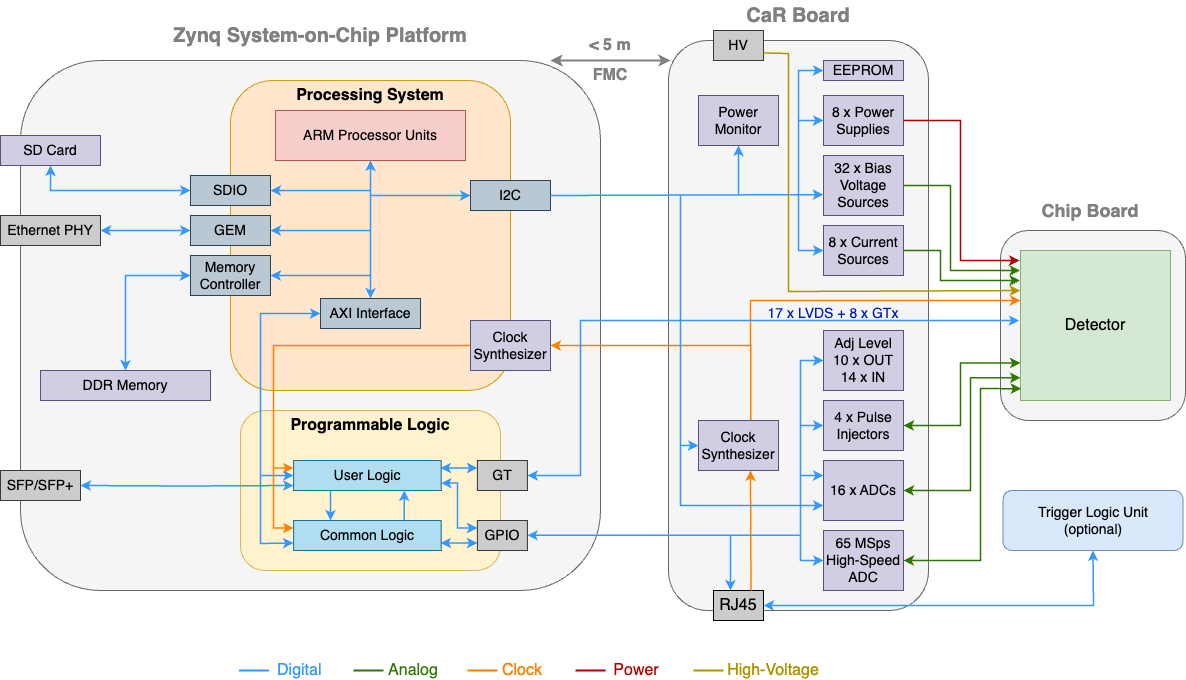

The Caribou hardware platform is anchored by the Control and Readout (CaR) board, a custom interface module that supplies all essential resources needed to operate and evaluate silicon pixel detector prototypes. It integrates a broad set of active and passive components—such as a clock synthesizer, programmable power supplies, single-ended and differential I/O links, high-speed data links, and both low- and high-speed ADCs—covering the full range of services required for device characterization. The CaR board connects to a supported System-on-Chip (SoC) platform through an FPGA Mezzanine Card (FMC) interface, with the option to use an FMC extension cable of up to 5 meters. A user-designed Detector Carrier Board — referred to as the Chip Board — attaches to the CaR board via a SEARAY connector, hosting the detector along with all required passive components.

MORE COMING SOON !