System Description

A brief description of the Caribou system

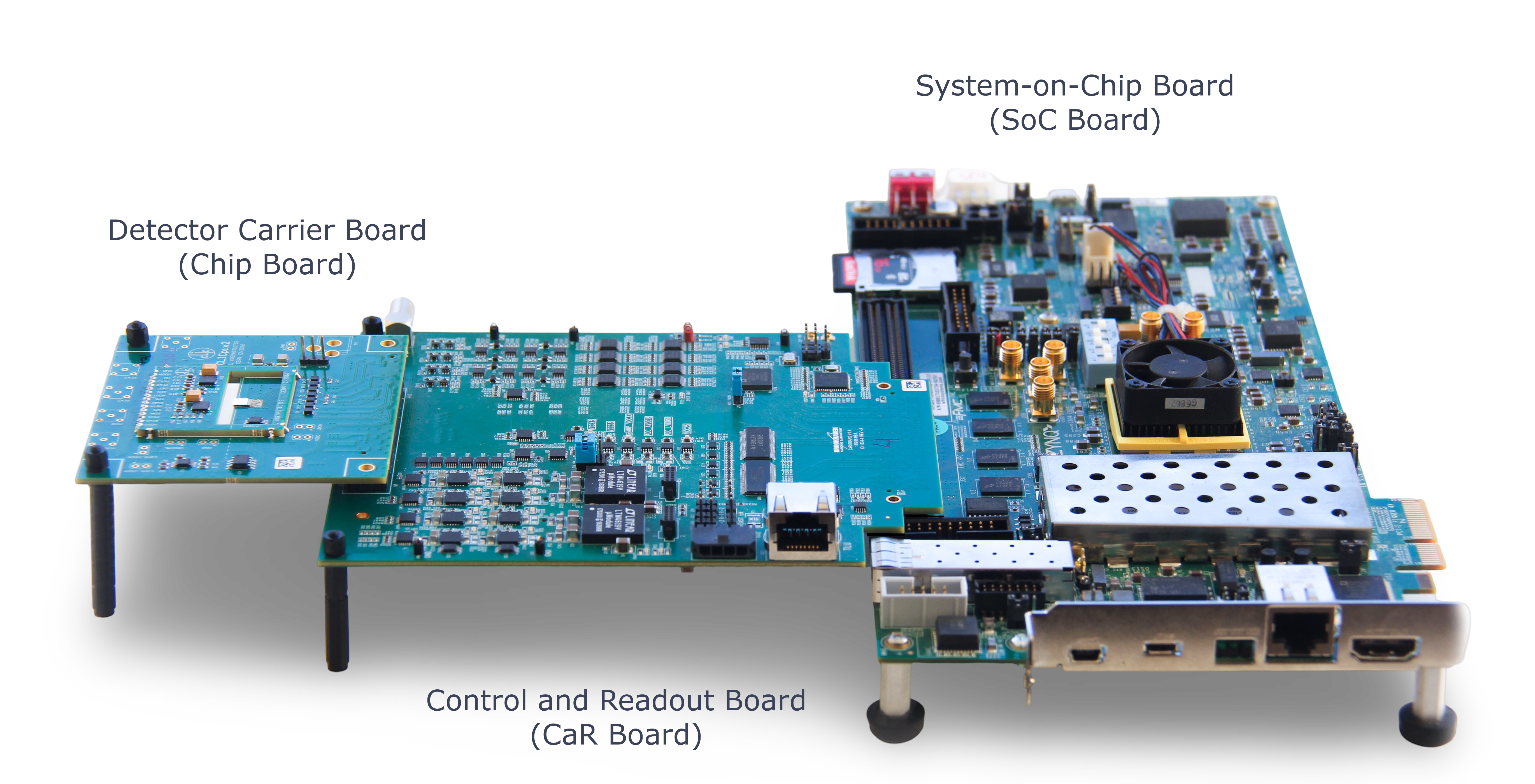

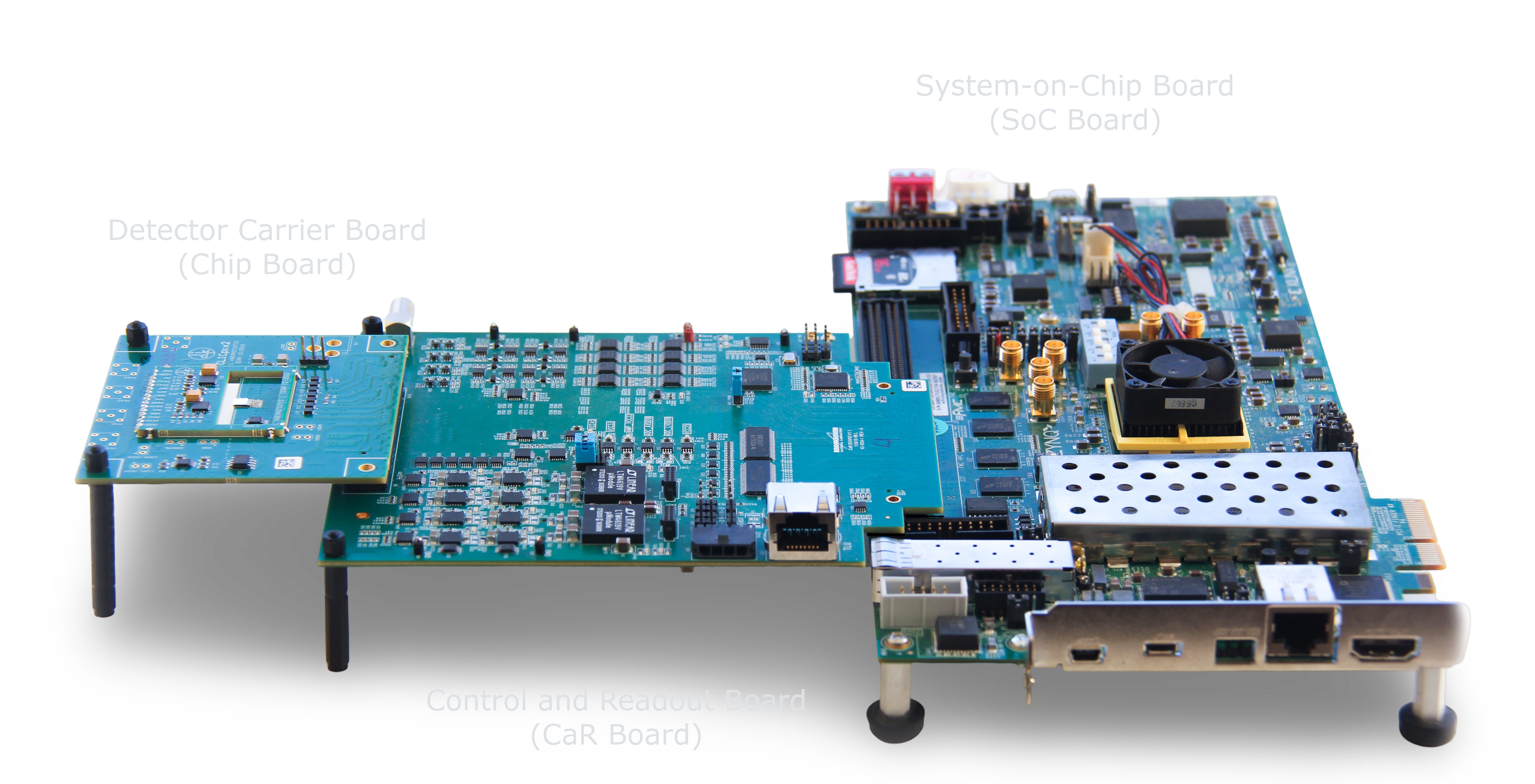

Caribou is a modular and highly flexible data acquisition system designed to accelerate the development and characterization of silicon pixel detector prototypes. At the heart of the system is the Control and Readout (CaR) board, a versatile hardware platform that provides all essential services required to operate a wide range of detector ASICs. These services include precision power delivery, biasing, slow-control infrastructure, and high-speed full-duplex GTX links reaching up to 12.5 Gbps. The CaR board interfaces directly with a Xilinx Zynq System-on-Chip (SoC) board, which runs a fully featured Yocto-based Linux distribution (Poky) and the Caribou data acquisition software stack, Peary.

In conventional detector R&D, each new prototype often requires the design of a dedicated readout board and the development of corresponding firmware and software—an effort that must be repeated whenever voltage levels, interface requirements, or data formats change. Caribou eliminates this repetition through a unified open-source architecture that is both reusable and easily extendable. Its combination of adaptable hardware, configurable firmware, and structured software interfaces provides a comprehensive environment for powering, controlling, and reading out diverse detector designs.

By supplying a ready-to-use suite of peripherals together with high-level control and DAQ software, Caribou significantly reduces the time needed to bring up new prototypes, debug issues, and collect first data. Its modular design ensures that the same system can be quickly retargeted to new devices once testing of a previous prototype is complete, thereby reducing development cost and improving overall workflow efficiency. As a result, Caribou has become a robust and widely adopted solution for detector R&D efforts requiring flexibility, rapid integration, and reliable performance.